A indústria da tecnologia acaba de presenciar um movimento que pode mudar a forma como os modelos de inteligência artificial (IA) acessam e processam os dados em larga escala. As gigantes Sandisk e a SK Hynix assinaram um memorando de entendimento (MoU) para desenvolver e padronizar o High Bandwidth Flash (HBF), uma tecnologia emergente que promete unir a persistência e a alta densidade da memória flash NAND com a arquitetura empilhada e de alta largura de banda do HBM (High Bandwidth Memory).

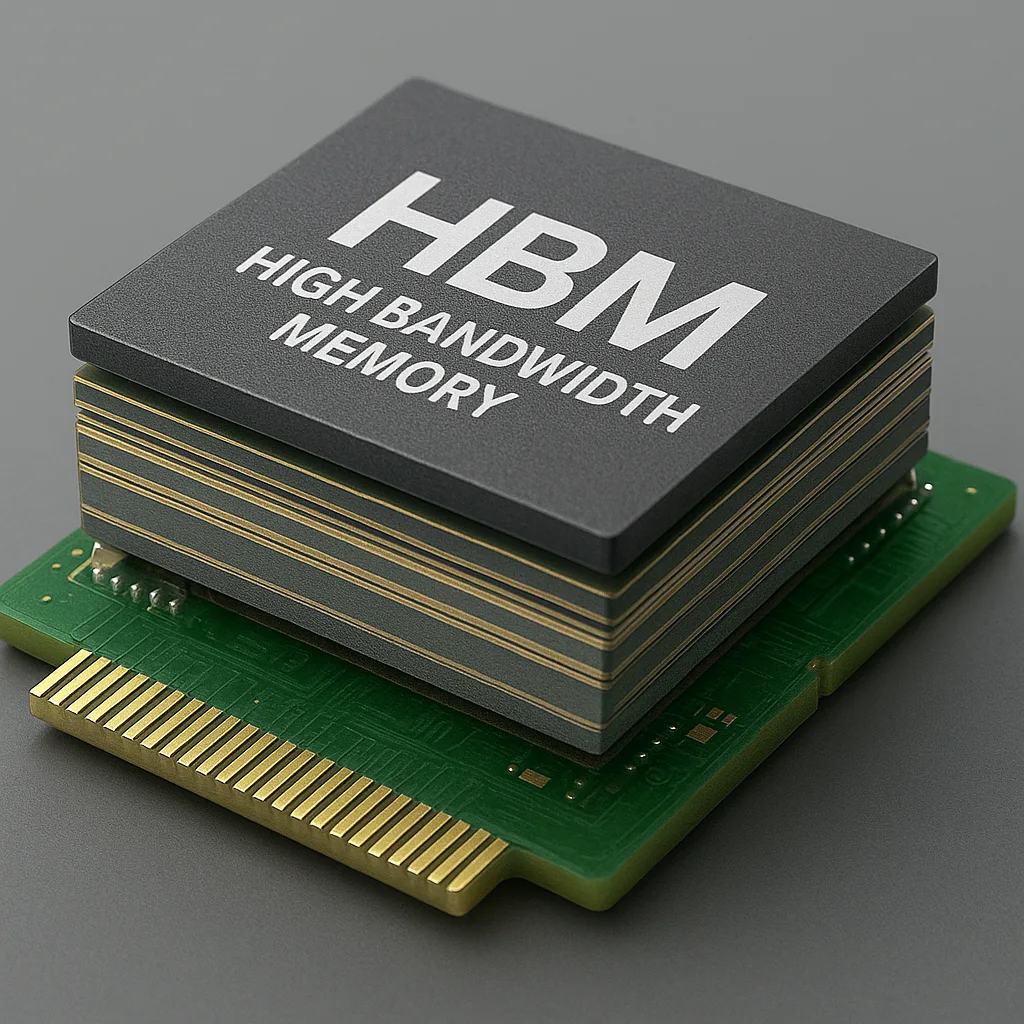

Para sabermos o quanto o HBF é revolucionário, é essencial entender o que é HBM (High Bandwidth Memory), a tecnologia que serviu de base para a sua concepção.

A HBM é uma memória DRAM empilhada em 3D e desenvolvida originalmente pela AMD e pela SK Hynix, projetada para fornecer taxas massivas de transferência de dados. Ela é amplamente usada em GPUs de última geração, chips de IA e supercomputadores.

- Aproveite as Ofertas!

Seu funcionamento é semelhante ao do HBF em alguns pontos, mas com uma diferença essencial: a HBM é volátil, ou seja, perde os dados ao ser desligada, enquanto o HBF, por ser baseado em NAND Flash, mantendo as informações gravadas.

A HBM empilha várias camadas de memória DRAM conectadas por TSVs montadas sobre um interposer que faz a comunicação direta com o processador. Essa estrutura reduz as distâncias físicas que os sinais elétricos percorrem, aumentando a velocidade e reduzindo o consumo energético.

As versões mais recentes, como a HB3e, podem alcançar os impressionantes 1,5 terabytes por segundos (TB/s) de largura de banda, tornando-se a espinha dorsal de GPUs uasadas por empresas como a NVIDIA, AMD e Intel.

Já o HBF, na prática, representa uma nova geração de memória híbrida criada para preencher a lacuna entre o armazenamento tradicional e as memórias voláteis ultrarrápidas, como a DRAM e a própria HBM. Ele busca equilibrar três pilares essenciais: velocidade, capacidade e eficiência energética, fatores críticos para sustentar a evolução de sistemas de inteligência artificial generativa e computação de alto desempenho (HPC).

Como o HBF funciona e porque é inovador

O Hight Bandwidth Flash (HBF) combina dois conceitos até então separados no mundo da computação:

- A persistência e a densidade da memória NAND Flash, base dos SSDs modernos.

- E a arquitetura empilhada e de computação paralela da HBM (High Bandwidth Memory) usada em GPUs e chips de IA

O segredo do HBF está em sua arquitetura tridimencional (3D stacking). Em vez de usar chips de memória dispostos lado a lado, o HBF empilha múltiplas camadas de memória flash verticalmente. Essas camadas são interconectadas por meio de estruturas chamadas TSVs (Through-Silicon Vias), que são pequenos canais condutores que permitem que os dados circulem de forma vertical e simultânea entre os chips e resultando, assim, em uma largura de banda muito superior à dos SSDs convencionais.

Além do mais, o HBF utiliza um interposer de silicio, uma base intermediária que conecta diretamente o conjunto de memórias ao processador (CPU, GPU ou ASIC). Essa ponte cria um caminho de comunicação extremamente rápido e reduz significativamente a latência de resposta entre leitura e escrita. O resultado é um desempenho muito próximo ao DRAM, mas com vantagem de armazenar os dados de forma permanente, mesmo sem energia.

Outro ponto técnico importante está no sistema de controle inteligente do HBF. A tecnologia flash tradicional sofre com maior latência na gravação de dados, algo que o HBF contorna por meio de controladores otimizados, buffers e até camadas de DRAM cache, que organizam e aceleram as operações de leitura e escrita. Isso permite que o HBF funcione como uma espécie de memória persistente ultrarrápida, ideal para processar grandes volumes de informação sem depender de acesso constante ao disco ou à rede.

- Garanta Agora!

Em termos práticos essa inovação traz benefícios claros:

- Largura de banda muito maior que a de SSDs NVMe;

- Baixa latência que acelera o processamento de IA e inferência de modelos;

- Alta densidade de armazenamento, permitindo mais dados em menos espaço;

- Eficiência energética superior em comparação às memórias voláteis de alta velocidade;

- Persistência de dados com garantia de integridade mesmo após desligamentos dos sistemas.

Essa combinação torna o HBF uma tecnologia ideal para treinar e rodar modelos de IA generativa, bancos de dados in-memory e arquiteturas que demandam acesso constante a informações em tempo real.

O HBM já é a base em GPUs e processadores avançados por oferecer largura de banda extrema, baixa latência e consumo otimizado. A inovação do HBF é incorporar parte dessas vantagens ao universo do flash NAND, criando uma solução híbrida que promete alta capacidade com eficiência energética.

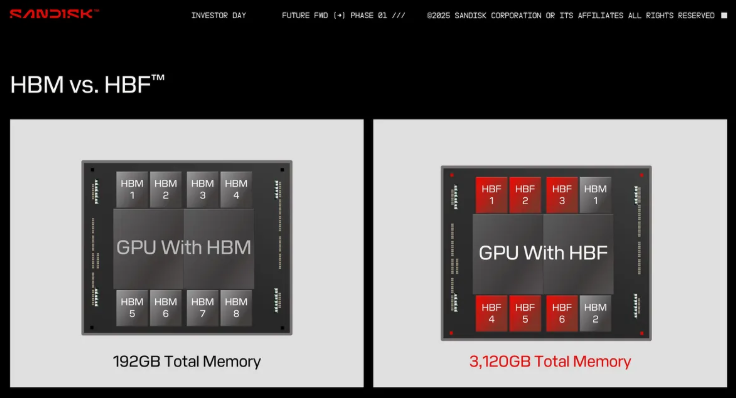

O HBF substitui parcialmente a DRAM tradicional usada no HBM por memória NAND, resultando em um aumento de capacidade de 8 a 16 vezes, mantendo largura de banda próxima à do HBM puro. Embora a latência seja ligeiramente maior, a troca compensa em cenários que exigem escalabilidade sem aumento proporcional no consumo de energia.

Outro ponto chave é a não volatilidade da NAND. Os dados permanecem mesmo sem alimentação elétrica, algo fundamental para data centers dedicados á Inteligência Artificial que operam em ambientes com limitações energéticas e térmicas. Essa abordagem ganha ainda mais relevância na borda da rede (edge), onde a eficiência é prioridade.

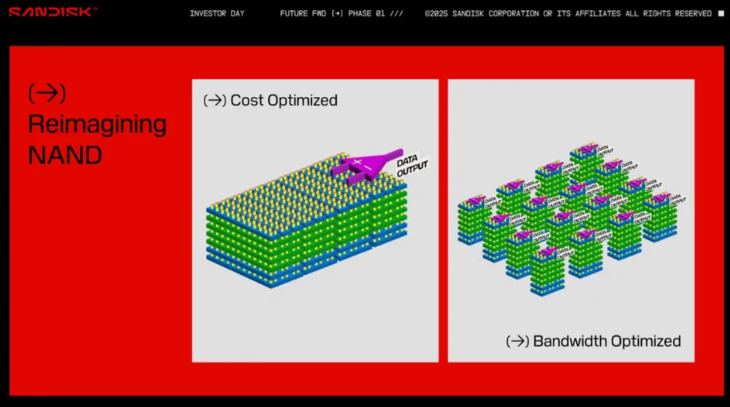

O protótipo da Sandisk

No Flash Memory Summit 2025, a Sandisk mostrou um protótipo promissor de HBF. Ele foi construído com a tecnologia BiCS NAND, que é um tipo de memória flash empilhada verticalmente para maximizar densidade e desempenho. Além disso, usa a arquitetura CBA (Circuit Bonding Architecture), que permite uma integração física compacta, possibilitando que o HBF ocupe espaços antes exclusivos para o HBM tradicional.

Essa junção de tecnologias mostra que o HBF não é apenas uma ideia, mas uma solução concreta, pronta para enfrentar os desafios das próximas gerações de data centers e dispositivos na borda da rede.

O HBF não surge por acaso, ele segue uma tendência do setor em buscar memórias mais versáteis para IA. O projeto já recebeu prêmios e criou um conselho consultivo técnico para definir padrões e estratégias abertas.

A previsão é que as amostras cheguem ao mercado em 2026 e que os primeiros produtos comerciais apareçam em 2027. Fabricantes como Nvidia podem adotar a tecnologia rapidamente, aproveitando a parceria histórica com a SK Hynix.

Leia também: Rumores revelam Intel Core Ultra 7 254V: o novo Lunar Lake

A presença de nomes como Raja Koduri no conselho do HBF indica ambições direto no design de chips para IA. Paralelamente, concorrentes como a Samsung trabalham em soluções próprias, como o PBSSD e o futuro HBM4.

O High Bandwidth Flash não é apenas mais um avanço incremental, ele sinaliza uma mudança de paradigma. Ao unir a alta largura de banda do HBM com a persistência e densidade do NAND, o HBF cria um novo tipo de memória capaz de reduzir custos, economizar energia e viabilizar aplicações antes limitadas pela disponibilidade da DRAM.

Se a padronização for bem sucedida, a tecnologia poderá se tornar onipresente em data centers, GPUs e dispositivos de borda, abrindo caminho para modelos de linguagem cada vez maiores e mais eficientes.

Mais do que atender à demanda atual, o HBF poderá atender a infraestrutura da IA para a próxima década, onde capacidade, eficiência e escalabilidade serão tão valiosas quanto o próprio poder de processamento.

Com a crescente demanda por modelos de Inteligência Artificial que exigem mais memória, o HBF oferece uma alternativa escalável e mais econômica para ampliar a memória de sistemas de inferência de IA, sem depender exclusivamente de soluções caras e energicamente intensivas como a DRAM pura.

Ele é especialmente útil em contextos onde há limitações térmicas e energéticas como data centers verdes ou dispositivos de inferência na borda da rede (edge).

Abaixo está uma tabela comparativa com o HBM, DRAM (DDR) e o novo HBF (High Bandwidth Flash), destacando suas principais características:

| Característica | HBM | DRAM (DDR) | HBF (High Bandwidth Flash) |

|---|---|---|---|

| Largura de banda | Muito alta | Moderada | Alta (similar ao HBM em algumas aplicações) |

| Consumo energético | Mais eficiente por bit | Mais alto | Muito eficiente, especialmente em cargas de inferência |

| Forma física | Empilhamento 3D com TSV | Chips laterais (2D) | Empilhamento 3D com NAND + arquitetura CBA |

| Persistência | Volátil | Volátil | Não volátil (mantém dados sem energia) |

| Capacidade | Limitada (até centenas de GB) | Limitada (escala com custo) | Muito alta (8–16× mais que HBM no mesmo espaço físico) |

| Custo | Alto | Mais acessível | Mais baixo que HBM por GB, mas ainda em validação |

| Latência | Muito baixa | Baixa | Moderada (maior que DRAM, menor que SSD tradicional) |

| Uso principal | IA, HPC, GPUs premium | PCs, servidores comuns | Inferência de IA, edge computing, data centers eficientes |